## TIE-50206 Logic Synthesis, Final Exam / Midterm Exam 2 Thu 4.3.2016 Page 1/3

|                                | - 1                                                                                                                                                                                                                                                                                                                             | IIu -                                                                                                                                                                                                                  | 7.0.20                                | 10                                                                                          |                                                 |                                                    |                   |              |             |     |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|-------------------|--------------|-------------|-----|

| Name:<br>Student               | no                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                        |                                       |                                                                                             |                                                 | -<br>-                                             |                   |              |             |     |

|                                | xam: Ans<br>dterm Exa                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                        |                                       | estion<br>nly question                                                                      | ns 4-6                                          |                                                    |                   |              |             |     |

| Studen<br>Moreov               | <i>r</i> er, each<br>heir stvle                                                                                                                                                                                                                                                                                                 | e any<br>stude<br>and t                                                                                                                                                                                                | calcula<br>ent can ha<br>hey are i    | tor or dict<br>ave 1 A4 s<br>not collect<br>wish with                                       | sheet of <b>o</b> v<br>ed.                      |                                                    | . There a         | ıre no restı | rictions    |     |

| In logic<br>arithme<br>Mark th | diagrams<br>tic compo<br>e name of                                                                                                                                                                                                                                                                                              | you onents fevery                                                                                                                                                                                                      | an use ba<br>(adder, su<br>signal ar  | oles, equati<br>asic gates (<br>ubtractor, m<br>nd indicate<br>numerical (<br>ssible, eli v | AND, OR nultiplier, co their width order (1a, 1 | ), flip-flops<br>omparator.<br>clearly.<br>lb, 6). | s, muitiple<br>). | exers, and o | common      |     |

| 1.                             | Answ<br>a)<br>b)                                                                                                                                                                                                                                                                                                                | Term                                                                                                                                                                                                                   | d explain<br>ns: signal<br>t is the d | 's event a                                                                                  | nd delta d<br>oetween a                         | elay (2p)<br>rchitecture                           | e types R         | RTL and st   | ructural (2 | 'p) |

| 2.                             | State a) b)                                                                                                                                                                                                                                                                                                                     | emachines(4p) Give an example how Mealy state machine differs from Moore state machine (2p) What are the basic styles to implement state machines with VHDL? What differences there are in practice between them? (2p) |                                       |                                                                                             |                                                 |                                                    |                   |              |             |     |

| 3.                             | Analyze the code in the following page. The clock period is 10 ns. (7p)  a) What errors or suspicious structures there are in the code? (There is no sy errors) (3p)  b) Fill in the timing diagram below directly according the code, i.e., without correcting any errors. Present the timing as simulator interprets it. (4p) |                                                                                                                                                                                                                        |                                       |                                                                                             |                                                 |                                                    |                   |              |             |     |

|                                | Stimulus<br>clk<br>rst_n<br>ctrl_in                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                        |                                       |                                                                                             |                                                 |                                                    |                   |              |             |     |

|                                | val_in                                                                                                                                                                                                                                                                                                                          | 000                                                                                                                                                                                                                    |                                       | 001                                                                                         |                                                 |                                                    |                   | 000          |             |     |

Fill in the response}

c\_out d\_out e\_out ninja

## TIE-50206 Logic Synthesis, Final Exam / Midterm Exam 2 Thu 4.3.2016 Page 2/3

```

Name:

Student no.

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric_std.all;

entity tentti is

generic (

data_width_g : integer := 3);

: in std logic;

clk

rst n : in std logic;

ctrl in : in std logic;

val_in : in std_logic_vector (data_width_g-1 downto 0);

c_out : out std_logic;

d_out : out std_logic_vector (data_width_g-1 downto 0);

e_out : out std_logic_vector (data_width_g-1 downto 0)

end tentti;

architecture gatelevel of tentti is

signal ninja: unsigned (data width g-1 downto 0);

begin

tenho: process (ctrl in, ninja, val in)

begin

if ctrl in = '1' then

e out <= not val in after 4 ns;

else

e out <= val in after 4 ns;

end if;

end process tenho;

sauren : process (clk, rst_n, ninja)

variable tmp_v : unsigned (3-1 downto 0);

begin

if rst n = '0' then

ninja \ll (others => '0');

elsif clk'event and clk = '1' then

tmp v := ninja+1;

d out <= std logic vector(tmp v);

ninja <= ninja +2;

end if;

end process sauren;

process (ninja)

begin

if to integer (ninja) = 6 then

c out <= '1';

else

c out <= '0';

end if;

end process;

--c out <= '0';

end gatelevel;

```

## TIE-50206 Logic Synthesis, Final Exam / Midterm Exam 2 Thu 4.3.2016 Page 3/3

| Name:       |   |  |  |  |

|-------------|---|--|--|--|

| Name.       | - |  |  |  |

| Student no. |   |  |  |  |

- 4. Analyze the VHDL code on the previous page. Show the resulting logic diagram after RTL syntehsis. Use dashed line to show separate synthesized logic of each process. Show every port, signal and variable. Don't make too small or ugly diagram, but clear and elegant. (6p)

- 5. Clocking (4p)

- a) What means the term *clock domain*? Draw a figure where it exists. What is the result of it or is there any results? (2p)

- b) Why would it be desirable to use many clock signals in the same chip? (2p)

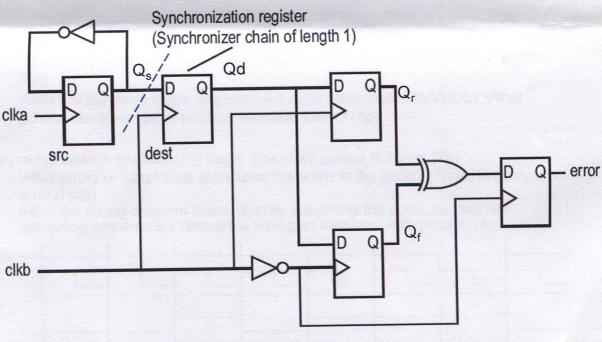

- 6. Analyze the test circuit below (5p)

- a) How the metastability is detected in basic RTL-simulation? (2p)

- b) How the test circuit works? (Hint: in addition to text, draw a small timing diagram where something interesting happens) (3p)

Figure 4. Test Circuit Structure for Metastability Characterization

Figure t5. Test Circuit