## TIE-50206 Logic Synthesis, Final Exam / Midterm Exam 2 Fri 3.3.2017 Page 1/3

| Name:       | Tell Commi |

|-------------|------------|

| Student no. |            |

Final Exam: Answer every question

2nd Midterm Exam: Answer only questions 3-5

Made by: Arto Perttula

Students can use **any calculator** or dictionary.

Moreover, each student can have 1 A4 sheet of **own notes**. There are no restrictions about their style and they are not collected.

Students can do anything they wish with the exam paper.

In addition to text, use figures, tables, equations, and examples in your answers. In logic diagrams, you can use basic gates (AND, OR...), flip-flops, multiplexers, and common arithmetic components (adder, subtractor, multiplier, comparator...). Mark the name of every signal and indicate their width clearly. Preferably write your answers in numerical order (1a, 1b, ... 5).

Please answer in Finnish if possible, eli vastaa suomeksi jos vain osaat.

- 1. Answer and explain (6p)

- a) Examples of VHDL-language structures that cannot be synthesized (never or sometimes) (2p)

- b) Show basic example (or two) how Mealy state machine can be implemented with VHDL-language (2p)

- c) What is the difference between loop-structures of programming language (like C) and hardware description language (like VHDL)? (2p)

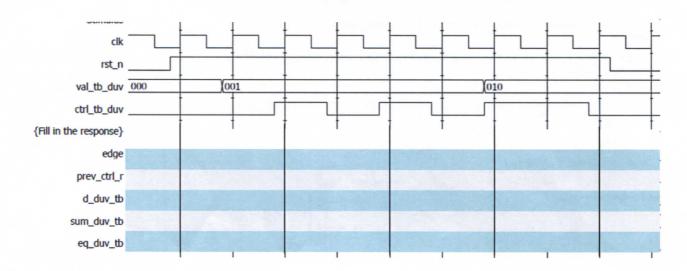

- 2. Analyze the code in the following page. The clock period is 10 ns. (9p)

- a) What errors or suspicious structures there are in the code? (4p)

- b) Fill in the timing diagram below directly according the code, i.e., without correcting any errors. Present the timing as simulator interprets it. (5p)

## TIE-50206 Logic Synthesis, Final Exam / Midterm Exam 2 Fri 3.3.2017 Page 2/3

Name: Student no. library ieee; use ieee.std logic 1164.all; use ieee.numeric\_std.all; use std.textio.all; entity tentti k14 is generic data width\_g: integer := 8); port ( : in std\_logic; : in std\_logic; : in std\_logic; : in std\_logic\_vector (data\_width\_g-1 downto 0); : out std\_logic\_vector (data\_width\_g-1 downto 0); : out std\_logic; rst n ctrl in val in sum out d out eq out : out std logic end tentti k14; architecture gatelevel of tentti k14 is -- accumulate signal sum\_r begin mike : process (clk, rst n) variable sum : integer; begin if rst\_n = '0' then sum\_r <= 0; d\_out <= '0'; elsif clk'event and clk = '1' then

d\_out <= '0';</pre> prev\_ctrl\_r <= ctrl\_in;

d\_out <= prev\_ctrl\_r;</pre> if edge = '1' then sum r <= to integer(unsigned (val in)) + sum r;</pre> end  $i\overline{f}$ ; end if; sum\_n end process mike; sumout sum out <= std logic\_vector (to\_unsigned (sum\_r, data\_width\_g));</pre> patton : process (val\_in, ctrl\_in, prev\_ctrl\_r, rst\_n) begin if (prev\_ctrl\_r = '0' and ctrl\_in='1') then edge <= '1';

else edge <= '0';</pre> Prev\_ctvl\_inend if; if std\_logic\_vector (to\_unsigned (sum\_r, data\_width\_g)) = val\_in then

eq\_out <= 'T1';</pre> else eq\_out <= '0';

end if;</pre> end process patton; end gatelevel; - eq - oct

## TIE-50206 Logic Synthesis, Final Exam / Midterm Exam 2 Fri 3.3.2017 Page 3/3

| Name:       |  |  |

|-------------|--|--|

| Student no. |  |  |

- 3. Analyze the VHDL code on the previous page. Show the resulting logic diagram after RTL syntehsis. Use dashed line to show separate synthesized logic of each process. Show every port, signal and variable. Don't make too small or ugly diagram, but clear and elegant. (6p)

- 3. Explain (5p)

- a) What is clock skew and how does it affect the FPGA's internal structure? (1p)

- b) What happens when reading a signal that is currently at value 'Z'? (1p)

- c) Why should entity's output be registered? (1p)

- d) Is it a good or bad idea that the same person writes both the DUV and TB? Why/why not? (1p)

- e) What are 3 main delivery types of an IP component? (1p)

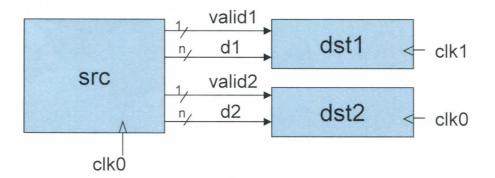

- 5. Analyze the circuit below. (4p)

- a) Which signals have to be synchonized? Or is it necessary to synchronize any of them? (2p)

- b) Is there enough signals for proper working? (2p)